# **AK4137**

# 32bit SRC with PCM/DSD conversion

#### 1. 概 要

AK4137 は 2ch のディジタルサンプルレートコンバータ(SRC)です。入力された 8kHz~768kHz の範囲にあるサンプルレートのオーディオソースを 8kHz~768kHz のサンプルレートに変換して出力します。また、発振器を内蔵しており、マスタクロックを必要としませんので、非常にシンプルな構成がとれます。ハイエンドオーディオ/USB DAC 等、異なるサンプルレートを持つ音源との接続用途に最適です。PCM-DSD 変換機能を持ち多彩な音楽再生が可能です。

|        | 2. 特 長                                                            |

|--------|-------------------------------------------------------------------|

|        | 2 channels input/output                                           |

|        | Asynchronous Sample Rate Converter                                |

|        | PCM                                                               |

|        | Input Sample Rate Range(FSI): 8kHz~768kHz                         |

|        | Output Sample Rate Range(FSO) : 8kHz~768kHz                       |

|        | Input to Output Sample Rate Ratio: FSO/FSI = 1/6~24               |

|        | DSD                                                               |

|        | Input Sample Rate Range(FSI): 2.8224MHz~12.288MHz                 |

|        | Output Sample Rate Range(FSO): 2.8224MHz~12.288MHz                |

|        | THD+N: Up to-150dB                                                |

|        | Dynamic Range: 186dB (A-weighted)                                 |

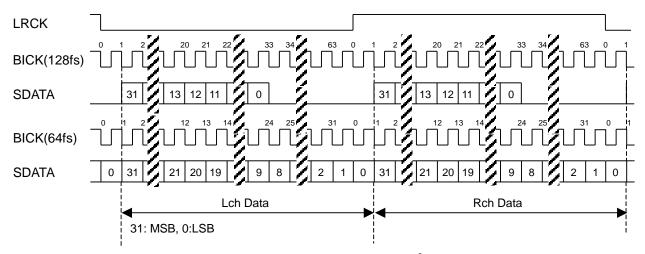

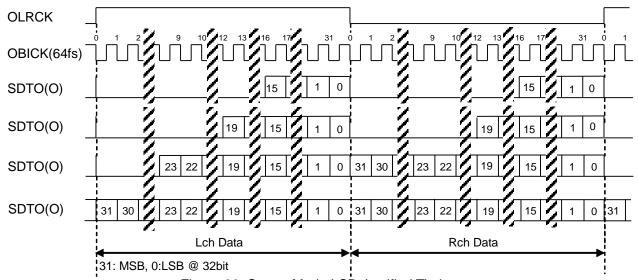

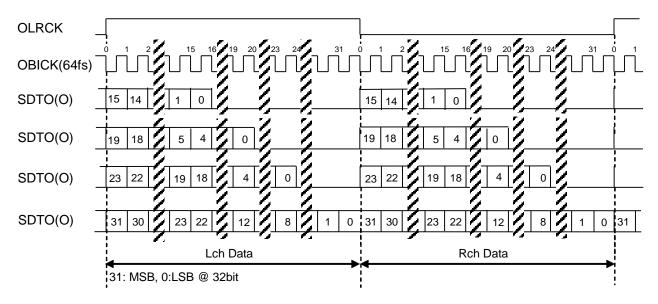

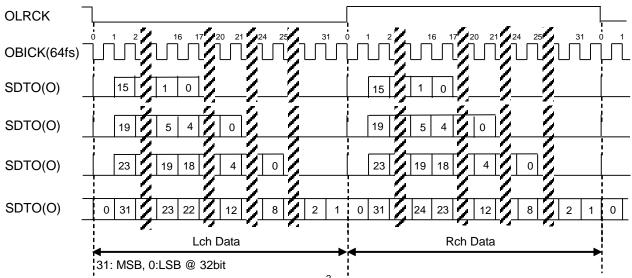

|        | I/F format : MSB justified, LSB justified, I2S compatible and TDM |

|        | PCM/DSD converter                                                 |

| _      | DoP I/F                                                           |

|        | Oscillator for Internal Operation Clock                           |

|        | Clock for Master mode : 64/128/192/256/384/512/768fso             |

|        | On-chip X'tal oscillator                                          |

|        | Digital De-emphasis Filter (32KHz, 44.1KHz, 48KHz)                |

| _      | soft Mute Function                                                |

|        | , , ,                                                             |

|        | uP Interface : I2C bus/SPI 4-wire                                 |

|        | Power Supply                                                      |

|        | DVDD: 3.0~3.6V (internal LDO enabled)                             |

|        | DVDD:1.7~1.9V (internal LDO disabled)                             |

| $\Box$ | Ta : -40∼+105°C                                                   |

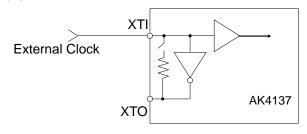

☐ Package: 48-pin LQFP (0.5mm pitch)

# 3. 目 次

| 1.                  | 概 要                                                       | 1    |

|---------------------|-----------------------------------------------------------|------|

| 2.                  | 特 長                                                       |      |

| 2.<br>3.            | 目 次                                                       |      |

| 4.                  | ローグ                                                       |      |

| <del></del> .<br>5. | ピン配置と機能説明                                                 |      |

| -                   | ナーダリングガイド                                                 |      |

|                     | 」 一                                                       |      |

|                     |                                                           |      |

| 6.                  | 絶対最大定格                                                    |      |

| 7.                  | 推奨動作条件                                                    |      |

| 8.                  | , , ,                                                     |      |

|                     | PCMIN->PCMOUT                                             |      |

|                     | ■ PCMIN->DSDOUT                                           |      |

|                     | ■ DSDIN->PCMOUT                                           |      |

| 9.                  |                                                           |      |

|                     | ■ 内蔵 LDO モード                                              |      |

|                     | ■ DV18 外部供給モード                                            | . 14 |

| 10.                 | フィルタ特性                                                    | . 15 |

|                     | ■ シャープロールオフ・フィルタ特性                                        | . 15 |

|                     | ■ スローロールオフ・フィルタ特性                                         |      |

|                     | ■ ショートディレイ・シャープロールオフ・フィルタ特性                               | . 17 |

|                     | ■ ショートディレイ・スローロールオフ・フィルタ特性                                | . 18 |

| 11.                 | DSD モード特性                                                 | . 19 |

|                     | ■ シャープロールオフ・フィルタ特性                                        | . 19 |

|                     | ■ スローロールオフ・フィルタ特性                                         |      |

|                     | ■ ショートディレイ・スローロールオフ・フィルタ特性                                |      |

| 12.                 |                                                           |      |

| 13.                 |                                                           |      |

| 14.                 |                                                           |      |

|                     | ■ タイミング波形                                                 |      |

| 15.                 |                                                           |      |

| _                   | ■ 動作モードと設定                                                |      |

|                     | ■ 幼1F C T C B C C C C C C C C C C C C C C C C             | _    |

|                     | ■ SRC バイパスモード                                             | . 39 |

|                     | ■ SNO バーバス ピード                                            |      |

|                     | ■ スレーラモード                                                 |      |

|                     | ■ マヘテモート<br>■ 入力ポートのシステムクロックとオーディオインタフェースフォーマット           |      |

|                     | ■ ハカポートのシステムクロックとオーティオインダフェースフォーマッド                       |      |

|                     | ■ 出力ポートのシステムグロックとモート設定                                    |      |

| _                   |                                                           |      |

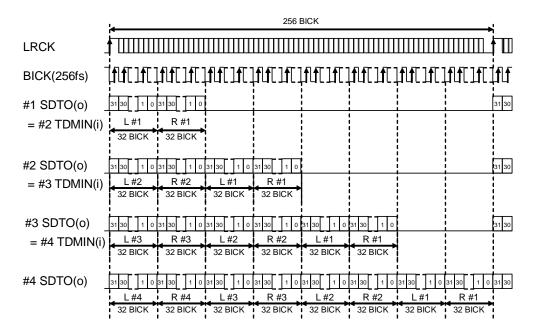

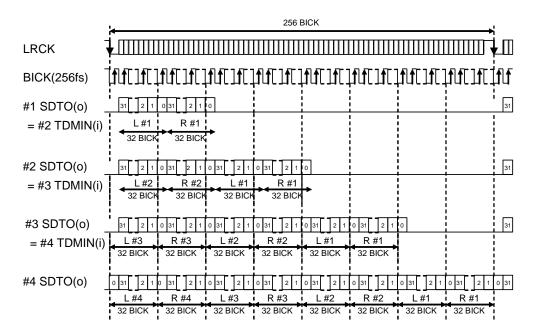

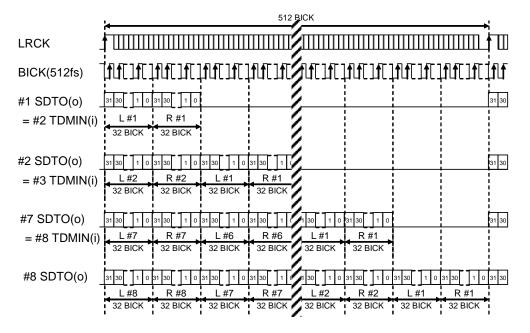

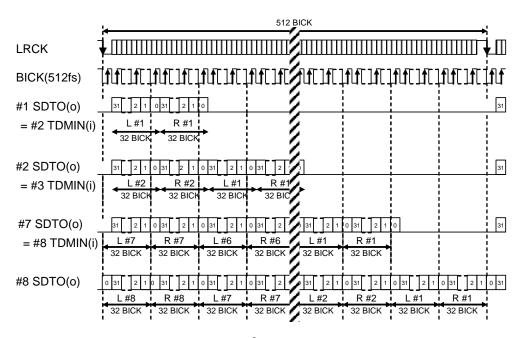

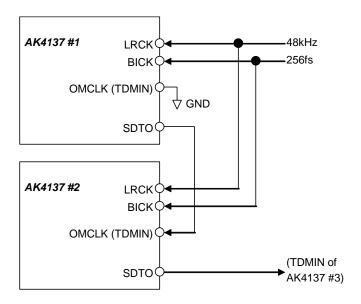

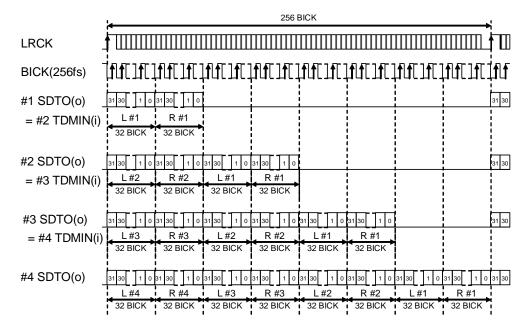

|                     | ■ TDM Mode 時のカスケード接続                                      |      |

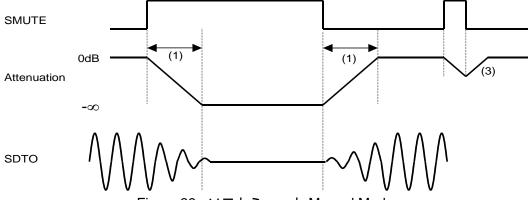

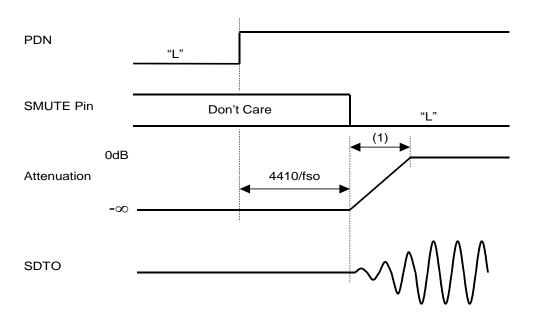

|                     | ■ ソフトミュート機能                                               |      |

|                     | ■ ディザ回路                                                   |      |

| _                   | ■ Digital フィルタ                                            | . 57 |

|                     | ■ ディエンファシスフィルタ                                            |      |

|                     | ■ レギュレータ                                                  |      |

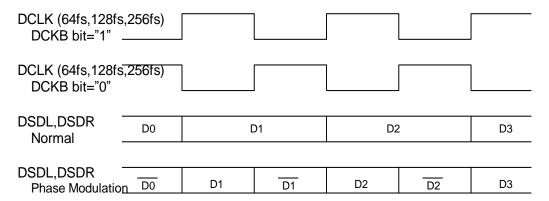

|                     | ■ DSD モード                                                 |      |

|                     | ■ クロック切り替えの手順                                             |      |

|                     | ■ PDN pin あるいは RSTN bit でリセットせずに入力ポートの ILRCK 周波数を変化させた場合  |      |

|                     | ■ PDN pin あるいは RSTN bit でリセットせずに出力ポートの OLRCK 周波数を変化させた場合. | . 62 |

| ■ レート変換時のポップノイズ除去              | 62 |

|--------------------------------|----|

| ■ 入力ソース切り替え (PCM⇔DSDI、DoP モード) |    |

| ■ 内部ステータスピン                    | 63 |

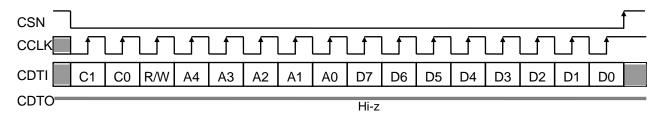

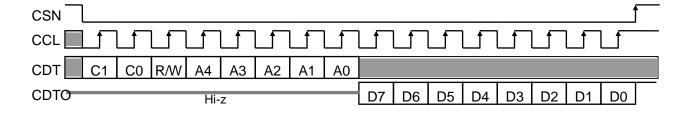

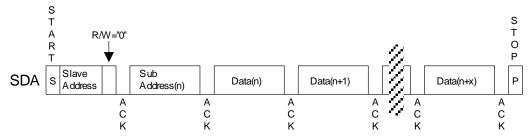

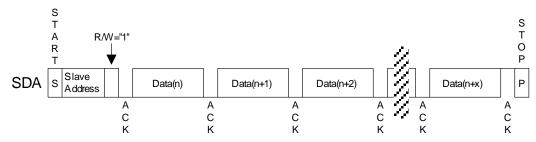

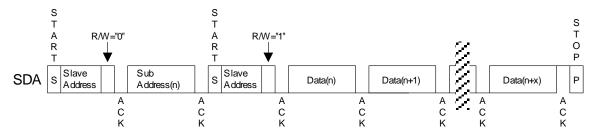

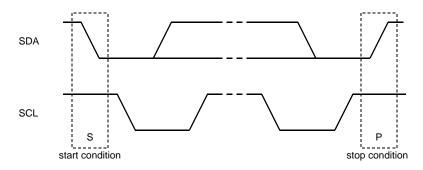

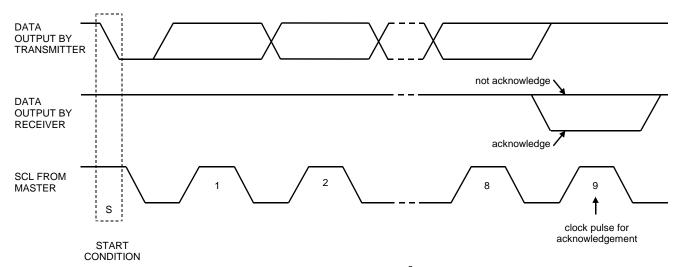

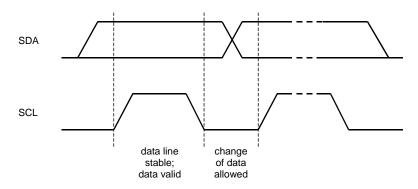

| ■ シリアルコントロールインタフェイス            |    |

| ■ レジスタマップ                      | 68 |

| ■ グラウンドと電源のデカップリング             | 74 |

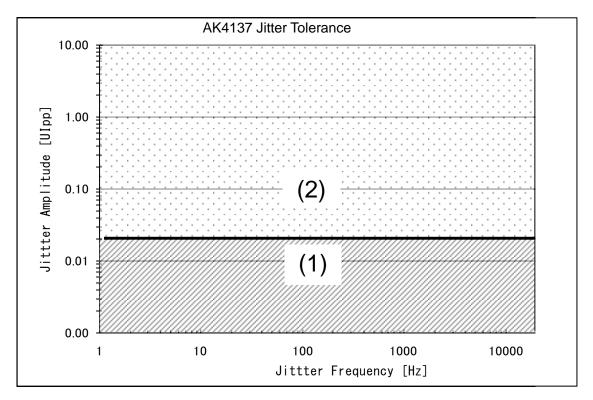

| 16. ジッター耐量                     |    |

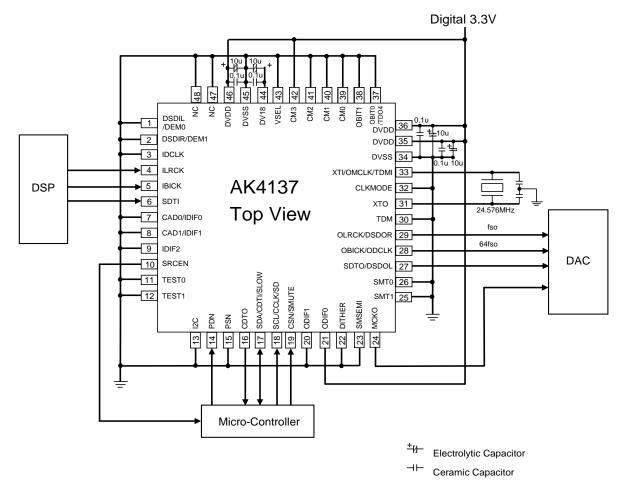

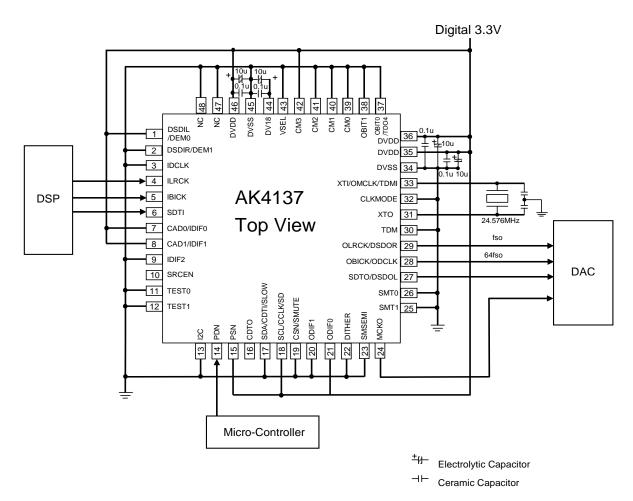

| 17. システム設計                     |    |

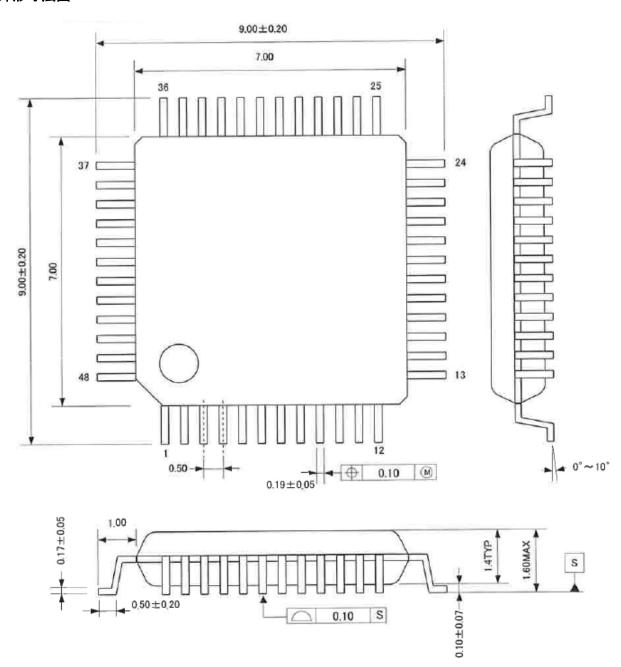

| 18. パッケージ                      | 78 |

| ■ 外形寸法図                        |    |

| ■ 材質・メッキ仕様                     | 78 |

| ■ マーキング                        | 79 |

| 19. 改訂履歴                       |    |

| 重要な注意事項                        | 81 |

|                                |    |

|                     | AK4137                       | AK4136                    |

|---------------------|------------------------------|---------------------------|

| bit                 | 32                           | ←                         |

| DR (A-Weighted)     | 186                          | 176                       |

| THD+N               | 150                          | 140                       |

| fsi                 | 8~768KHz                     | 8∼384KHz                  |

| fso                 | 8~768KHz                     | 8~384KHz                  |

| Ratio I/O           | 1/6~24                       | 1/6~12                    |

| 出力側クロック<br>(マスタ動作用) | 64/128/256/384/512/768fso 対応 | 128/256/384/512/768fso 対応 |

| SRC 変換              | PCM→PCM 変換、DSD→DSD 変換        | PCM→PCM 変換                |

|                     | DSD→PCM 変換、PCM→DSD 変換        |                           |

|                     | DoP→DSD 変換、DoP→PCM 変換        |                           |

| SRC バイパス機能          | あり (マスタ、スレーブ)                | ←                         |

| ソフトミュート             | あり                           | あり                        |

|                     | セミオートモード                     | セミオートモード、                 |

|                     | ミュート時間設定可能                   | ミュート時間設定はレジスタ設定のみ         |

| DITHER              | あり                           | あり(レジスタ設定のみ)              |

| 内蔵レギュレータ            | 3V→1.8V                      | ←                         |

| 外部 1.8V 入力          | あり                           | ←                         |

| 水晶発振回路              | あり                           | ←                         |

| レート変換時<br>ポップノイズ除去  | あり                           | <b>←</b>                  |

| マイコン I/F            | I2C、4Wire                    | ←                         |

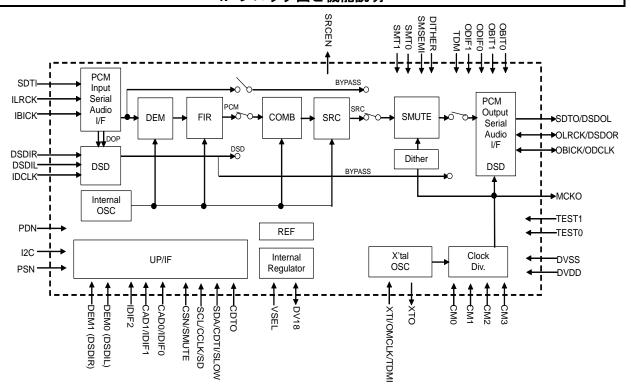

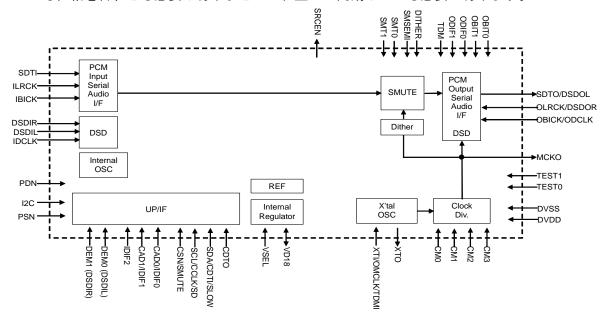

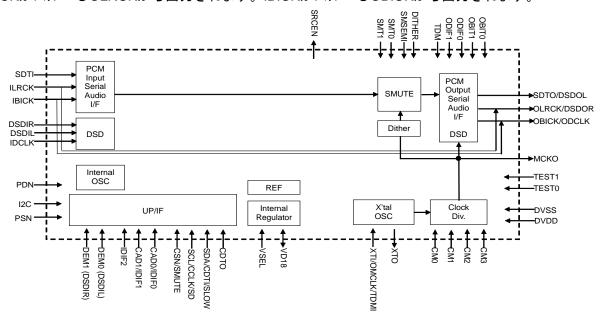

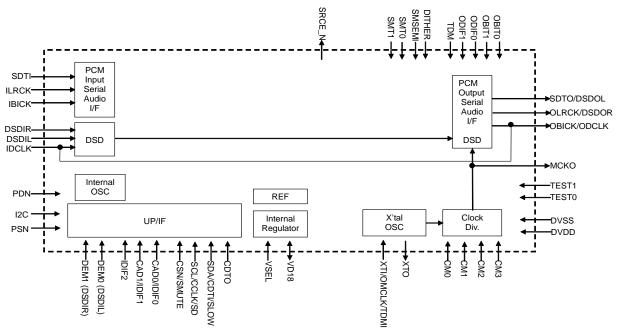

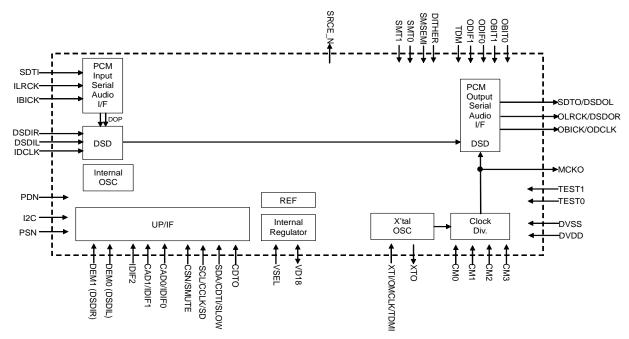

# 4. ブロック図と機能説明

Figure 1. ブロック図

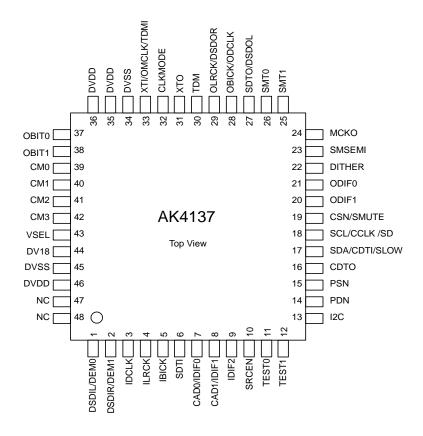

### 5. ピン配置と機能説明

## オーダリングガイド

AK4137EQ  $-40 \sim +85^{\circ}$ C 48pin LQFP (0.5mm pitch) AKD4137 AK4137評価用ボード

Figure 2. ピン配置

## ■ ピン機能説明

| No.  | Pin Name | I/O  | Function                                                       |  |  |

|------|----------|------|----------------------------------------------------------------|--|--|

| INU. |          | 1/0  |                                                                |  |  |

| 1    | DSDIL    | <br> | DSD Data Pin in DSD Mode                                       |  |  |

|      | DEM0     | ı    | De-emphasis Control #0 Pin                                     |  |  |

| 2    | DSDIR    |      | DSD Data Pin in DSD Mode                                       |  |  |

|      | DEM1     | I    | De-emphasis Control #1 Pin                                     |  |  |

| 3    | IDCLK    | I    | DSD Clock Pin in DSD Mode                                      |  |  |

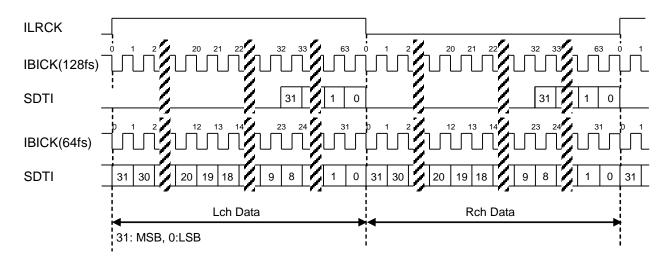

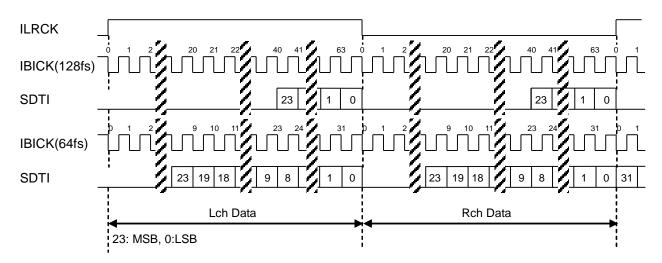

| 4    | ILRCK    | I    | L/R Clock Pin in PCM Mode                                      |  |  |

| 5    | IBICK    | I    | Audio Serial Data Clock Pin in PCM Mode                        |  |  |

| 6    | SDTI     | I    | Audio Serial Data Input Pin in PCM Mode                        |  |  |

| 7    | CAD0     | l    | Chip Address 0 Pin in Serial Control Mode                      |  |  |

| '    | IDIF0    | ı    | Digital Input Format 0 Pin in Parallel Control Mode            |  |  |

|      | CAD1     | ı    | Chip Address 1 Pin in Serial Control Mode                      |  |  |

| 8    | IDIF1    | l    | Digital Input Format 1 Pin in Parallel Control Mode            |  |  |

| 9    | IDIF2    |      | gital Input Format 2 Pin in Parallel Control Mode              |  |  |

| 10   | SRCEN    | EN O | Unlock Status Pin                                              |  |  |

| 10   | SKCEN    | )    | When the PDN pin= "L", this pin outputs "H".                   |  |  |

| 11   | TEST0    | I    | Test pin 0. Must be connected to DVSS in normal use.           |  |  |

| 12   | TEST1    | ı    | Test pin 1. Must be connected to DVSS in normal use.           |  |  |

| 40   | 100      |      | Select serial mode                                             |  |  |

| 13   | 3   I2C  | ı    | "L": 4-wire serial Mode ,"H": I2C Mode                         |  |  |

|      |          |      | Power-Down Mode Pin                                            |  |  |

|      |          |      | "H": Power up,                                                 |  |  |

| 14   | PDN      | I    | "L": Power down reset and initializes the control register.    |  |  |

|      |          |      | The AK4137 should be reset once by bringing PDN pin = "L" upon |  |  |

|      |          |      | power-up.                                                      |  |  |

| 15   | PSN      |      | Parallel/Serial Mode Select                                    |  |  |

| 15   | POIN     | 1    | "L": Serial Mode , "H": Parallel Mode                          |  |  |

Note 1. 全ての入力ピンはオープンにしないでください。DVDD は同じ電源に繋いでください。 Note 2. PSN, CM3-0, OBIT1-0, TDM, ODIF1-0, IDIF2-0 and CAD1-0 pin must be changed when the PDN pin = "L".

| No. | Pin Name   | I/O | Function                                                                                                                                            |

|-----|------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 16  | CDTO       | 0   | I2C= "L": Control Data Output Pin in Serial Control Mode                                                                                            |

|     | SDA        | I/O | I2C= "H": Control Data In/Out Pin in Serial Control Mode                                                                                            |

| 17  | CDTI       | ı   | I2C= "L": Control Data Input Pin in Serial Control Mode                                                                                             |

|     | SLOW       | I   | Digital Filter Select Pin in Parallel Control Mode                                                                                                  |

|     | SCL        | I   | I2C= "H": Control Data Clock Input Pin in Serial Control Mode                                                                                       |

| 18  | CCLK       | I   | I2C= "L": Control Data Clock Pin in Serial Control Mode                                                                                             |

|     | SD         | I   | Digital Filter Select Pin in Parallel Control Mode                                                                                                  |

|     | CSN        | I   | Chip Select Pin in Serial Control Mode , I2C= "L"                                                                                                   |

| 19  | SMUTE      | I   | Soft Mute Pin in Parallel Control Mode When this pin is changed to "H", soft mute cycle is initiated. When returning "L", the output mute releases. |

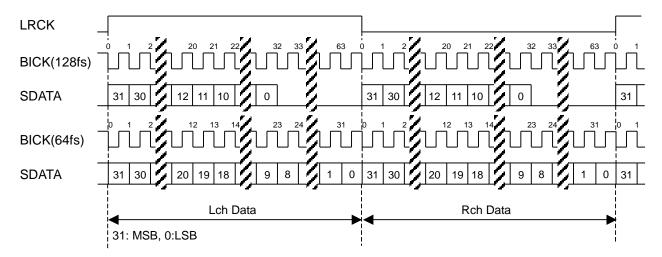

| 20  | ODIF1      | - 1 | Audio Interface Format #1 Pin for Output PORT                                                                                                       |

| 21  | ODIF0      | I   | Audio Interface Format #0 Pin for Output PORT                                                                                                       |

| 22  | DITHER     | I   | Dither Enable Pin  "H": Dither ON, "L": Dither OFF                                                                                                  |

| 22  | SMSEMI     | ı   | Soft Mute Semi Auto Mode                                                                                                                            |

| 23  | SIVISEIVII | ı   | "L": Manual Mode , "H": Semi Auto Mode                                                                                                              |

| 24  | MCKO       | 0   | Master Clock Output Pin                                                                                                                             |

| 25  | SMT1       | I   | Soft Mute Timer select #1 Pin                                                                                                                       |

| 26  | SMT0       | - 1 | Soft Mute Timer select #0 Pin                                                                                                                       |

| 27  | SDTO O     |     | Audio Serial Data Output Pin for Output PORT When the PDN pin = "L", the SDTO pin outputs "L".                                                      |

| 21  | DSDOL      | 0   | DSD Data Pin in DSD Mode                                                                                                                            |

|     | DODOL      |     | Audio Serial Data Clock Pin for Output PORT                                                                                                         |

| 28  | OBICK      | I/O | When the PDN pin = "L" in master mode, the OBICK pin outputs "L".                                                                                   |

|     | ODCLK      | I/O | DSD Clock Pin in DSD Mode                                                                                                                           |

| 29  | OLRCK      | I/O | Output Channel Clock Pin for Output PORT When the PDN pin = "L" in master mode, the OLRCK pin outputs "L".                                          |

|     | DSDOR      | 0   | DSD Data Pin in DSD Mode                                                                                                                            |

| 30  | TDM        | I   | TDM Format Select Pin  "L"(connected to DVSS): Stereo Mode  "H"(connected to DVDD): TDM mode for Output                                             |

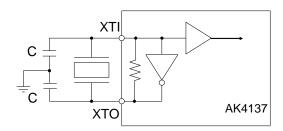

| 31  | хто        | 0   | X'tal Output Pin When the PDN pin = "L" or CM3-0 = "LHHL" or "LHHH" or "Hxxx" XTO outputs "L".                                                      |

| 32  | CLKMODE    | _   | Master Clock Select Pin  "L"(connected to DVSS): X'tal Mode  "H"(connected to DVDD): External Master Clock or TDM="H"                               |

Note 1. 全ての入力ピンはオープンにしないでください。DVDD は同じ電源に繋いでください。

Note 2. PSN, CM3-0, OBIT1-0, TDM, ODIF1-0, IDIF2-0 and CAD1-0 pin must be changed when the PDN pin = "L".

| No.                  | Pin Name | I/O   | Function                                                                    |      |     |                                                              |  |  |                                                                      |

|----------------------|----------|-------|-----------------------------------------------------------------------------|------|-----|--------------------------------------------------------------|--|--|----------------------------------------------------------------------|

|                      | XTI      | ı     | X'tal Input Pin                                                             |      |     |                                                              |  |  |                                                                      |

| 33                   | OMCLK    | I     | External Master Clock Input                                                 |      |     |                                                              |  |  |                                                                      |

|                      | TDMI     | I     | TDMI Daisy-Chain Input Pin                                                  |      |     |                                                              |  |  |                                                                      |

| 34                   | DVSS     | ı     | Digital Ground Pin                                                          |      |     |                                                              |  |  |                                                                      |

| 35                   | DVDD     | ı     | Digital Power Supply Pin, 3.0 ~ 3.6V or 1.7 ~ 1.9V                          |      |     |                                                              |  |  |                                                                      |

| 36                   | DVDD     | ı     | Digital Power Supply Pin, 3.0 ~ 3.6V or 1.7 ~ 1.9V                          |      |     |                                                              |  |  |                                                                      |

| 37                   | OBIT0    |       | Bit Length Select #0 Pin for Output Data                                    |      |     |                                                              |  |  |                                                                      |

| 38                   | OBIT1    |       | Bit Length Select #1 Pin for Output Data                                    |      |     |                                                              |  |  |                                                                      |

| 39                   | CM0      | -     | Clock Select or Mode Select #0 Pin for Output PORT                          |      |     |                                                              |  |  |                                                                      |

| 40                   | CM1      |       | Clock Select or Mode Select #1 Pin for Output PORT                          |      |     |                                                              |  |  |                                                                      |

| 41                   | CM2      |       | Clock Select or Mode Select #2 Pin for Output PORT                          |      |     |                                                              |  |  |                                                                      |

| 42                   | CM3      |       | Clock Select or Mode Select #3 Pin for Output PORT                          |      |     |                                                              |  |  |                                                                      |

| Digital Power select |          |       |                                                                             |      |     |                                                              |  |  |                                                                      |

| 45                   | VOLL     | '     | "L": DV18 is Output pin, "H": DV18 is Power Supply Pin                      |      |     |                                                              |  |  |                                                                      |

|                      |          |       | Digital Power Pin, Typ 1.8V                                                 |      |     |                                                              |  |  |                                                                      |

|                      |          |       | VSEL= "L", Output                                                           |      |     |                                                              |  |  |                                                                      |

|                      | DV/10    | D\/18 | D\/19                                                                       | DV18 |     |                                                              |  |  | When the PDN pin= "L", the DV18 pin outputs "L". Current must not be |

| 44                   |          |       |                                                                             |      | I/O | taken from this pin. A 10µF (±30%; including the temperature |  |  |                                                                      |

| 44                   | DVIO     | 1/0   | characteristics) capacitor should be connected between this pin and         |      |     |                                                              |  |  |                                                                      |

|                      |          |       | DVSS. When this capacitor is polarized, the positive polarity pin should be |      |     |                                                              |  |  |                                                                      |

|                      |          |       | connected to the DV18 pin.                                                  |      |     |                                                              |  |  |                                                                      |

|                      |          |       | VSEL= "H", Input                                                            |      |     |                                                              |  |  |                                                                      |

| 45                   | DVSS     | -     | Digital Ground Pin                                                          |      |     |                                                              |  |  |                                                                      |

| 46                   | DVDD     | -     | Digital Power Supply Pin, 3.0 ~ 3.6V or 1.7 ~ 1.9V                          |      |     |                                                              |  |  |                                                                      |

| 47                   | NC       | -     | This pin must be connected to DVSS.                                         |      |     |                                                              |  |  |                                                                      |

| 48                   | NC       | ı     | This pin must be connected to DVSS.                                         |      |     |                                                              |  |  |                                                                      |

Note 1. 全ての入力ピンはオープンにしないでください。DVDD は同じ電源に繋いでください。 Note 2. PSN, CM3-0, OBIT1-0, TDM, ODIF1-0, IDIF2-0 and CAD1-0 pin must be changed when the PDN pin = "L".

# \*使用しない入出カピン

| 区分      | ピン名                          | 設定                 |

|---------|------------------------------|--------------------|

|         | SMSEMI, DITHER,<br>CSN/SMUTE | DVSS に接続           |

| Digital | XTI/OMCLK/TDMI               | DVSS に接続 (スレーブモード) |

|         | SRCEN, MCKO, XTO, CDTO       | オープン               |

\*PDN pin = "L"の時、I/O ピンの状態は次の通り規定されます。(マスタモード時は"L"出力になります。) AK4137 は CM3 pin = "H"の時、必ず出力になります。

| 設定ピ | ン   |     |     | OLRCK, |

|-----|-----|-----|-----|--------|

| CM3 | CM2 | CM1 | CM0 | OBICK  |

| L   | L   | L   | L   |        |

| L   | L   | L   | Н   | "L"出力  |

| L   | L   | Н   | L   | L田刀    |

| L   | L   | Н   | Η   |        |

| L   | Н   | L   | L   | 入力     |

| L   | Н   | L   | Н   |        |

| L   | Н   | Н   | L   | "L"出力  |

| L   | Н   | Н   | Н   | ᆫᆅᄭ    |

| Н   | -   | -   | -   |        |

\*PDN pin = "L"の時、出力ピンの状態は次の通り規定されます。

| 出カピン  | 状態    |

|-------|-------|

| SDTO  | "L"出力 |

| SRCEN | "H"出力 |

| MCKO  | "L"出力 |

| XTO   | "L"出力 |

| CDTO  | Hi-z  |

#### 6. 絶対最大定格

(DVSS=0V; Note 3)

|                                              | Parameter                   | Symbol | Min. | Max.     | Unit |

|----------------------------------------------|-----------------------------|--------|------|----------|------|

| Power Supplies                               | Digital                     | DVDD   | -0.3 | 4.3      | V    |

|                                              | (Internal Digital) (Note 4) | DV18   | -0.3 | 2.5      | V    |

| Input Current, Any Pin Except Supplies       |                             | IIN    | ı    | ±10      | mA   |

| Digital Input Voltage (Note 5)               |                             | VDIN   | -0.3 | DVDD+0.3 | V    |

| Ambient Temperature (Power applied) (Note 6) |                             | Ta     | -40  | 105      | °C   |

| Storage Tempera                              | ture                        | Tstg   | -65  | 150      | °C   |

Note 3. 電圧は全てグラウンドに対する値です。

Note 4. DVSS は同じベタグラウンドに接続してください。

Note 5. DSDIL/DEM0, DSDIR/DEM1, ILRCK,IBICK, DCLK, SDTI, IDIF0/CAD0, IDIF1/CAD1, IDIF2, PDN, PSN, I2C, SLOW/CDTI/SDA, SD/CCLK/SCL, SMUTE/CSN, SMSEMI, SMT1-0, OBIT1-0, ODIF1-0,CM3-0, DITHER, VSEL, TEST1-0 pin

Note 6. 実装されるプリント基板の配線密度は 100%以上にしてください。

注意: この値を超えた条件で使用した場合、デバイスを破壊することがあります。 また通常の動作は保証されません。

#### 7. 推奨動作条件

(DVSS=0V; Note 3; VSEL= "L")

| Parameter      |         | Symbol | Min. | Тур. | Max. | Unit |

|----------------|---------|--------|------|------|------|------|

| Power Supplies | Digital | DVDD   | 3.0  | 3.3  | 3.6  | V    |

(DVSS=0V; Note 3; VSEL= "H")

| Parameter                      |                    | Symbol       | Min.       | Тур.       | Max.       | Unit   |

|--------------------------------|--------------------|--------------|------------|------------|------------|--------|

| Power<br>Supplies:<br>(Note 7) | Digital<br>Digital | DVDD<br>DV18 | 1.7<br>1.7 | 1.8<br>1.8 | 1.9<br>1.9 | V<br>V |

|                                | Difference         | DVDD- DV18   | -          | 0          | -          | V      |

Note 3. 電圧は全てグラウンドに対する値です。

Note 7. DVDD と DV18 は外部で接続してください。

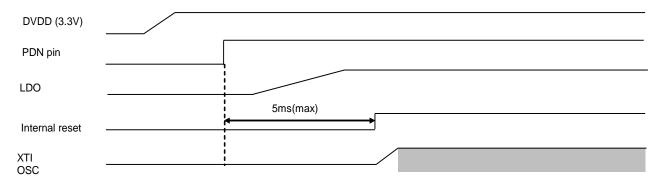

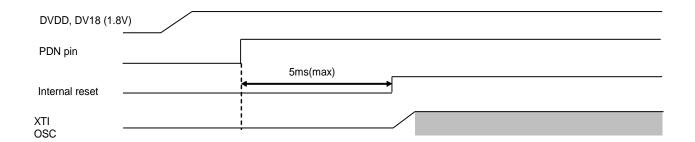

電源はPDN pin = "L"の状態で各電源を立ち上げ、電源が立ち上がった後、PDN pin = "H"にしてください。 マイコンの書き込みはPDN pin "↑"後、5ms後、行って下さい。

## 8. SRC 特性

#### **■ PCMIN->PCMOUT**

(Ta=-40~ +105°C; DVDD=3.0~3.6V or DVDD=DV18=1.7V~1.9V; DVSS=0V; Signal Frequency=1KHz; data = 32bit; measurement bandwidth = 20Hz~FSO/2; unless otherwise specified.)

| Parameter   |                                     | Symbol  | Min. | Тур. | Max. | Unit |

|-------------|-------------------------------------|---------|------|------|------|------|

| Resolution  |                                     |         |      |      | 32   | Bits |

| Input Samp  | le Rate                             | FSI     | 8    |      | 768  | kHz  |

| Output Sam  | ple Rate                            | FSO     | 8    |      | 768  | kHz  |

| THD+N       | (Input= 1kHz, 0dBFS)                |         |      |      |      |      |

|             | FSO/FSI=44.1kHz/48kHz               |         | -    | -150 | -    | dB   |

|             | FSO/FSI=48kHz/44.1kHz               |         | -    | -133 | -    | dB   |

|             | FSO/FSI=48kHz/192kHz                |         | -    | -153 | -    | dB   |

|             | FSO/FSI=192kHz/48kHz                |         | -    | -144 | -    | dB   |

|             | Worst Case (FSO/FSI=32kHz/176.4kHz) |         | -    | -    | -111 | dB   |

| Dynamic Ra  | ange (Input= 1kHz, -60dBFS)         |         |      |      |      |      |

|             | FSO/FSI=44.1kHz/48kHz               |         | -    | 184  | -    | dB   |

|             | FSO/FSI=48kHz/44.1kHz               |         | -    | 183  | -    | dB   |

|             | FSO/FSI=48kHz/192kHz                |         | -    | 184  | -    | dB   |

|             | FSO/FSI=192kHz/48kHz                |         | -    | 184  | -    | dB   |

|             | Worst Case (FSO/FSI= 48kHz/32kHz)   |         | 176  | -    | -    | dB   |

| Dynamic Ra  | ange                                |         |      |      |      |      |

| (Input= 1k  | (Input= 1kHz, -60dBFS, A-weighted)  |         |      |      |      |      |

|             | FSO/FSI=44.1kHz/48kHz               |         | -    | 186  | -    | dB   |

| Ratio betwe | en Input and Output Sample Rate     | FSO/FSI | 1/6  |      | 24   | -    |

#### **■ PCMIN->DSDOUT**

(Ta=-40 $^{\circ}$  +105 $^{\circ}$ C; DVDD=3.0 $^{\circ}$ 3.6V or DVDD=VD18=1.7 $^{\circ}$ 1.9V; DVSS=0V; Signal Frequency=1KHz; data = 32bit; measurement bandwidth = 20Hz $^{\circ}$  FSO/2; unless otherwise specified.)

| Parameter                    |                                   | Symbol  | Min. | Тур. | Max. | Unit |

|------------------------------|-----------------------------------|---------|------|------|------|------|

| Resolution                   |                                   |         |      | 32   | Bits |      |

| Input Sample                 | Rate                              | FSI     | 8    |      | 768  | kHz  |

| Output Sampl                 | le Rate                           | FSO     | 44.1 |      | 48   | kHz  |

| THD+N                        | (Input= 1kHz, 0dBFS, Note 8)      |         |      |      |      |      |

|                              | 64FSO/FSI=2.822MHz/44.1kHz        |         | -    | -115 | -    | dB   |

|                              | 128FSO/FSI=5.6448MHz/44.1kHz      |         | -    | -119 | -    | dB   |

|                              | 256FSO/FSI=11.2896MHz/176.4kHz    |         | -    | -123 | -    | dB   |

| Dynamic Ran                  | ge (Input= 1kHz, -60dBFS, Note 8) |         |      |      |      |      |

|                              | 64FSO/FSI=2.822MHz /44.1kHz       |         | -    | 116  | -    | dB   |

| 128FSO/FSI=5.6448MHz/44.1kHz |                                   |         | -    | 119  | -    | dB   |

|                              |                                   | -       | 123  | -    | dB   |      |

| Ratio between                | n Input and Output Sample Rate    | FSO/FSI | 1/16 |      | 1    | -    |

Note 8. OGAINM6 bit = "1"

#### **■ DSDIN->PCMOUT**

(Ta=-40~ +105°C; DVDD=3.0~3.6V or DVDD=VD18=1.7~1.9V; DVSS=0V; Signal Frequency=1KHz; data = 32bit; measurement bandwidth = 20Hz~ FSO/2; unless otherwise specified.)

| Parameter    |                                            | Symbol  | Min. | Тур. | Max.  | Unit |  |

|--------------|--------------------------------------------|---------|------|------|-------|------|--|

| Resolution   | Resolution                                 |         |      |      | 32    | Bits |  |

| Input Sample | Rate                                       | FSI     | 44.1 |      | 48 kF |      |  |

| Output Samp  | ole Rate                                   | FSO     | 44.1 |      | 768   | kHz  |  |

| THD+N        | (Input= 1kHz, -6dBFS, Note 9)              |         |      |      |       |      |  |

|              | FSO/64FSI =44.1kHz/2.8224MHz               |         | -    | -98  | -     | dB   |  |

|              | FSO/128FSI =44.1kHz/5.6448MHz              |         | -    | -115 | -     | dB   |  |

|              | FSO/256FSI = 44.1kHz/11.2896MHz            |         | -    | -115 | -     | dB   |  |

| Dynamic Rar  | nge (Input= 1kHz, -60dBFS, Note 9)         |         |      |      |       |      |  |

|              | FSO/64FSI =44.1kHz/2.8224MHz               |         | -    | 108  | -     | dB   |  |

|              | FSO/128FSI =44.1kHz/5.6448MHz              |         | -    | 140  | -     | dB   |  |

|              | FSO/256FSI =44.1kHz/11.2896MHz             |         | -    | 132  | -     | dB   |  |

| Dynamic Rar  | nge                                        |         |      |      |       |      |  |

| (Input= 1kHz | (Input= 1kHz, -60dBFS, A-weighted, Note 9) |         |      |      |       | dB   |  |

|              | FSO/128FSI =44.1kHz/5.6448MHz -            |         |      |      | -     |      |  |

| Ratio betwee | n Input and Output Sample Rate             | FSO/FSI | 1    |      | 17.4  | -    |  |

Note 9. IGAINM6 bit = "1". AK4137 の DSD 出力をソースとして定義。

#### **■ DSDIN->DSDOUT**

(Ta=-40~ +105°C; DVDD=3.0~3.6V or DVDD=VD18=1.7~1.9V; DVSS=0V; Signal Frequency=1KHz; data = 32bit; measurement bandwidth = 20Hz~ FSO/2; unless otherwise specified.)

| Parameter                                     | Symbol   | Min. | Тур. | Max. | Unit |

|-----------------------------------------------|----------|------|------|------|------|

| Resolution                                    |          |      |      | 32   | Bits |

| Input Sample Rate                             | FSI      | 44.1 |      | 48   | kHz  |

| Output Sample Rate                            | FSO      | 44.1 |      | 48   | kHz  |

| THD+N (Input= 1kHz, -6dBFS, Note 10)          |          |      |      |      |      |

| 64FSO/64FSI =2.8224MHz/2.8224MHz              |          | -    | -111 | -    | dB   |

| 128FSO/128FSI =5.6448MHz/5.6448MHz            |          | -    | -115 | -    | dB   |

| 256FSO/256FSI =11.2896MHz/11.2896MHz          | <u>,</u> | -    | -115 | -    | dB   |

| Dynamic Range (Input= 1kHz, -60dBFS, Note 10) |          |      |      |      |      |

| 64FSO/64FSI =2.8224MHz/2.8224MHz              |          | -    | 116  | -    | dB   |

| 128FSO/128FSI =5.6448MHz/5.6448MHz            |          | -    | 119  | -    | dB   |

| 256FSO/256FSI =11.2896MHz/11.2896MHz          | <u>:</u> | -    | 123  | -    | dB   |

| Ratio between Input and Output Sample Rate    | FSO/FSI  | 1    |      | 1    | -    |

Note 10. \*IGAINM6 bit = "1", OGAINM6 bit = "1"

## 9. 消費電流

## ■ 内蔵 LDO モード

(Ta=-40~ +105°C; DVDD=3.0~3.6V)

| Parame                   | ter                                      | Symbol | Min. | Тур. | Max. | Unit |

|--------------------------|------------------------------------------|--------|------|------|------|------|

| Power Supply Current     | Power Supply Current                     |        |      |      |      |      |

| Normal operation: (PDN = | "H")                                     |        |      |      |      |      |

| FSI=FSO=48kHz at Maste   |                                          | -      | 11   | -    | mA   |      |

| FSI=FSO=192kHz at Mas    | FSI=FSO=192kHz at Master Mode: DVDD=3.3V |        |      | 33   | -    | mA   |

| FSI=FSO=768kHz at Mas    | ter Mode: DVDD=3.3V                      |        | -    | 40   | -    | mA   |

|                          | : DVDD=3.6V                              |        | -    | -    | 60   | mA   |

| Power down: PDN = "L"    | (Note 11)                                |        |      |      |      |      |

|                          | DVDD=3.6V                                |        |      | 10   | 100  | μΑ   |

Note 11. クロックピンを含めた全てのディジタル入力が DVSS と同電位のとき。

### ■ DV18 外部供給モード

(Ta=-40~ +105°C; DVDD=DV18=1.7~1.9V)

| Parameter                                     | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------------------------------|--------|------|------|------|------|

| Power Supply Current                          |        |      |      |      |      |

| Normal operation:                             |        |      |      |      |      |

| FSI=FSO=48kHz at Master Mode: DVDD=DV18=1.8V  |        | -    | 11   | -    | mΑ   |

| FSI=FSO=192kHz at Master Mode: DVDD=DV18=1.8V |        | -    | 28   | -    | mΑ   |

| FSI=FSO=768kHz at Master Mode: DVDD=DV18=1.8V |        | -    | 32   | -    | mΑ   |

| : DVDD=DV18=1.9V                              |        | -    | -    | 50   | mΑ   |

| Power down: PDN = "L" (Note 11)               |        |      |      |      |      |

| DVDD=DV18=1.9V                                |        |      | 10   | 100  | μΑ   |

Note 11. クロックピンを含めた全てのディジタル入力が DVSS と同電位のとき。

# 10. フィルタ特性

# ■ シャープロールオフ・フィルタ特性

| Parameter      |                                | Symbol | Min.      | Тур.     | Max.      | Unit |

|----------------|--------------------------------|--------|-----------|----------|-----------|------|

| Digital Filter |                                | , ,    |           | <u> </u> | L         |      |

| Passband       | 0.985 ≤ FSO/FSI ≤ 24.000       | PB     | 0         | _        | 0.4583FSI | kHz  |

| -0.01dB        | 0.905 ≤ FSO/FSI < 0.985        | PB     | 0         | _        | 0.4167FSI | kHz  |

|                | 0.714 ≤ FSO/FSI < 0.905        | PB     | 0         | _        | 0.3195FSI | kHz  |

|                | 0.656 ≤ FSO/FSI < 0.714        | PB     | 0         | _        | 0.2852FSI | kHz  |

|                | 0.536 ≤ FSO/FSI < 0.656        | PB     | 0         | _        | 0.2182FSI | kHz  |

|                | 0.492 ≤ FSO/FSI < 0.536        | PB     | 0         | _        | 0.2177FSI | kHz  |

|                | 0.452 ≤ FSO/FSI < 0.492        | PB     | 0         | _        | 0.1948FSI | kHz  |

|                | 0.357 ≤ FSO/FSI < 0.452        | PB     | 0         | _        | 0.1458FSI | kHz  |

|                | 0.324 ≤ FSO/FSI < 0.357        | PB     | 0         | _        | 0.1302FSI | kHz  |

|                | 0.246 ≤ FSO/FSI < 0.324        | PB     | 0         | _        | 0.0917FSI | kHz  |

|                | 0.226 ≤ FSO/FSI < 0.246        | PB     | 0         | -        | 0.0826FSI | kHz  |

|                | 0.1667 ≤ FSO/FSI < 0.226       | PB     | 0         | _        | 0.0583FSI | kHz  |

| Stopband       | 0.985 ≤ FSO/FSI ≤ 24.000       | SB     | 0.5417FSI | _        | -         | kHz  |

|                | 0.905 ≤ FSO/FSI < 0.985        | SB     | 0.5021FSI | -        | -         | kHz  |

|                | 0.714 ≤ FSO/FSI < 0.905        | SB     | 0.3965FSI | -        | -         | kHz  |

|                | 0.656 ≤ FSO/FSI < 0.714        | SB     | 0.3643FSI | -        | -         | kHz  |

|                | $0.536 \le FSO/FSI < 0.656$    | SB     | 0.2974FSI | -        | -         | kHz  |

|                | $0.492 \le FSO/FSI < 0.536$    | SB     | 0.2813FSI | -        | -         | kHz  |

|                | $0.452 \le FSO/FSI < 0.492$    | SB     | 0.2604FSI | -        | -         | kHz  |

|                | 0.357 ≤ FSO/FSI < 0.452        | SB     | 0.2116FSI | -        | -         | kHz  |

|                | $0.324 \le FSO/FSI < 0.357$    | SB     | 0.1969FSI | ı        | -         | kHz  |

|                | $0.246 \le FSO/FSI < 0.324$    | SB     | 0.1573FSI | ı        | -         | kHz  |

|                | 0.226 ≤ FSO/FSI < 0.246        | SB     | 0.1471FSI | -        | -         | kHz  |

|                | 0.1667 ≤ FSO/FSI < 0.226       | SB     | 0.1020FSI | -        | -         | kHz  |

| Passband       | 0.226 ≤ FSO/FSI ≤24.000        | PR     | -         | -        | ±0.01     | dB   |

| Ripple         | 0.1667 ≤ FSO/FSI < 0.226       | PR     | -         | -        | ±0.03     | dB   |

| Stopband       | $0.985 \le FSO/FSI \le 24.000$ | SA     | 140.2     | -        | -         | dB   |

| Attenuation    | 0.905 ≤ FSO/FSI < 0.985        | SA     | 140.9     | -        | -         | dB   |

|                | 0.714 ≤ FSO/FSI < 0.905        | SA     | 135.2     | -        | -         | dB   |

|                | 0.656 ≤ FSO/FSI < 0.714        | SA     | 135.1     | -        | -         | dB   |

|                | 0.536 ≤ FSO/FSI < 0.656        | SA     | 133.5     | -        | -         | dB   |

|                | 0.492 ≤ FSO/FSI < 0.536        | SA     | 115.3     | -        | -         | dB   |

|                | 0.452 ≤ FSO/FSI < 0.492        | SA     | 118.2     | -        | -         | dB   |

|                | 0.357 ≤ FSO/FSI < 0.452        | SA     | 123.3     | -        | -         | dB   |

|                | 0.324 ≤ FSO/FSI < 0.357        | SA     | 122.9     | -        | -         | dB   |

|                | 0.246 ≤ FSO/FSI < 0.324        | SA     | 117.9     | -        | -         | dB   |

|                | 0.226 ≤ FSO/FSI < 0.246        | SA     | 119.7     | -        | -         | dB   |

| 0              | 0.1667 ≤ FSO/FSI < 0.226       | SA     | 90.3      | -        | -         | dB   |

| Group Delay    |                                | GD     | -         | 64       | -         | 1/fs |

| (Note 12)      | <br>                           |        |           |          |           |      |

Note 12. 入力と出力の位相ずれがない時の、L, R のデータが入力された後の ILRCK の立ち上がりから、L, R データを出力する前の OLRCK の立ち上がりまでの期間です。

## ■ スローロールオフ・フィルタ特性

| Parameter            |                           | Symbol | Min.      | Тур.  | Max.      | Unit |

|----------------------|---------------------------|--------|-----------|-------|-----------|------|

| Digital Filter       |                           |        |           |       |           |      |

| Passband -0.01dB     | 0.1667 ≤ FSO/FSI < 24.000 | PB     | 0         | -     | 0.0417FSI | kHz  |

| Stopband             | 0.1667 ≤ FSO/FSI < 24.000 | SB     | 0.4167FSI | -     |           | kHz  |

| Passband Ripple      |                           | PR     | -         | -     | ±0.01     | dB   |

| Stopband Attenuation |                           | SA     | -         | 108.1 | -         | dB   |

| Group Delay          | (Note 12)                 | GD     | -         | 64    | -         | 1/fs |

Note 12. 入力と出力の位相ずれがない時の、L, R のデータが入力された後の ILRCK の立ち上がりから、L, R データを出力する前の OLRCK の立ち上がりまでの期間です。

# ■ ショートディレイ・シャープロールオフ・フィルタ特性

| Parameter      | 0 C , DVDD=3.0~3.0V 01 DVDL    | Symbol | Min.                 | Typ.     | Max.           | Unit |

|----------------|--------------------------------|--------|----------------------|----------|----------------|------|

| Digital Filter |                                |        | <u> </u>             | <u> </u> | <u>L</u>       |      |

| Passband       | 0.985 ≤ FSO/FSI ≤ 24.000       | PB     | 0                    | -        | 0.4583FSI      | kHz  |

| -0.01dB        | 0.905 ≤ FSO/FSI < 0.985        | PB     | 0                    | -        | 0.4167FSI      | kHz  |

|                | 0.714 ≤ FSO/FSI < 0.905        | PB     | 0                    | -        | 0.3195FSI      | kHz  |

|                | 0.656 ≤ FSO/FSI < 0.714        | PB     | 0                    | -        | 0.2852FSI      | kHz  |

|                | 0.536 ≤ FSO/FSI < 0.656        | PB     | 0                    | -        | 0.2182FSI      | kHz  |

|                | 0.492 ≤ FSO/FSI < 0.536        | PB     | 0                    | -        | 0.2177FSI      | kHz  |

|                | 0.452 ≤ FSO/FSI < 0.492        | PB     | 0                    | -        | 0.1948FSI      | kHz  |

|                | 0.357 ≤ FSO/FSI < 0.452        | PB     | 0                    | -        | 0.1458FSI      | kHz  |

|                | 0.324 ≤ FSO/FSI < 0.357        | PB     | 0                    | -        | 0.1302FSI      | kHz  |

|                | 0.246 ≤ FSO/FSI < 0.324        | PB     | 0                    | -        | 0.0917FSI      | kHz  |

|                | 0.226 ≤ FSO/FSI < 0.246        | PB     | 0                    | -        | 0.0826FSI      | kHz  |

|                | 0.1667 ≤ FSO/FSI < 0.226       | PB     | 0                    | -        | 0.0583FSI      | kHz  |

| Stopband       | 0.985 ≤ FSO/FSI ≤ 24.000       | SB     | 0.5417FSI            | -        | -              | kHz  |

|                | 0.905 ≤ FSO/FSI < 0.985        | SB     | 0.5021FSI            | -        | -              | kHz  |

|                | 0.714 ≤ FSO/FSI < 0.905        | SB     | 0.3965FSI            | -        | -              | kHz  |

|                | 0.656 ≤ FSO/FSI < 0.714        | SB     | 0.3643FSI            | -        | -              | kHz  |

|                | 0.536 ≤ FSO/FSI < 0.656        | SB     | 0.2974FSI            | -        | -              | kHz  |

|                | 0.492 ≤ FSO/FSI < 0.536        | SB     | 0.2813FSI            | -        | -              | kHz  |

|                | 0.452 ≤ FSO/FSI < 0.492        | SB     | 0.2604FSI            | -        | -              | kHz  |

|                | 0.357 ≤ FSO/FSI < 0.452        | SB     | 0.2116FSI            | -        | -              | kHz  |

|                | $0.324 \le FSO/FSI < 0.357$    | SB     | 0.1969FSI            | -        | -              | kHz  |

|                | $0.246 \le FSO/FSI < 0.324$    | SB     | 0.1573FSI            | -        | -              | kHz  |

|                | $0.226 \le FSO/FSI < 0.246$    | SB     | 0.1471FSI            | -        | -              | kHz  |

|                | 0.1667 ≤ FSO/FSI < 0.226       | SB     | 0.1020FSI            | -        | -              | kHz  |

| Passband       | $0.226 \le FSO/FSI \le 24.000$ | PR     | -                    | -        | ±0.01          | dB   |

| Ripple         | 0.1667 ≤ FSO/FSI < 0.226       | PR     | -                    | -        | ±0.03          | dB   |

| Stopband       | $0.985 \le FSO/FSI \le 24.000$ | SA     | 140.2                | -        | -              | dB   |

| Attenuation    | $0.905 \le FSO/FSI < 0.985$    | SA     | 140.9                | -        | -              | dB   |

|                | 0.714 ≤ FSO/FSI < 0.905        | SA     | 135.2                |          | -              | dB   |

|                | $0.656 \le FSO/FSI < 0.714$    | SA     | 135.1                | -        | -              | dB   |

|                | $0.536 \leq FSO/FSI < 0.656$   | SA     | 133.5                | -        | -              | dB   |

|                | $0.492 \le FSO/FSI < 0.536$    | SA     | 115.3                | -        | -              | dB   |

|                | 0.452 ≤ FSO/FSI < 0.492        | SA     | 118.2                | -        | -              | dB   |

|                | 0.357 ≤ FSO/FSI < 0.452        | SA     | 123.3                | -        | -              | dB   |

|                | 0.324 ≤ FSO/FSI < 0.357        | SA     | 122.9                | -        | -              | dB   |

|                | 0.246 ≤ FSO/FSI < 0.324        | SA     | 117.9                | -        | -              | dB   |

|                | 0.226 ≤ FSO/FSI < 0.246        | SA     | 119.7                | -        | -              | dB   |

|                | 0.1667 ≤ FSO/FSI < 0.226       | SA     | 90.3                 | -        | -              | dB   |

|                | 0.905 ≤ FSO/FSI ≤ 24.000       | GD     | -                    | 20       | -              | 1/fs |

|                | 0.656 ≤ FSO/FSI < 0.905        | GD     | -                    | 22       | -              | 1/fs |

|                | 0.536 ≤ FSO/FSI < 0.656        | GD     | -                    | 26       | -              | 1/fs |

| 0 5:           | 0.492 ≤ FSO/FSI < 0.536        | GD     | -                    | 23       | -              | 1/fs |

| Group Delay    | 0.452 ≤ FSO/FSI < 0.492        | GD     | -                    | 24       | -              | 1/fs |

| (Note 12)      | 0.324 ≤ FSO/FSI < 0.452        | GD     | -                    | 26       | -              | 1/fs |

|                | 0.246 ≤ FSO/FSI < 0.324        | GD     | -                    | 29       | -              | 1/fs |

|                | 0.226 ≤ FSO/FSI < 0.246        | GD     | -                    | 30       | -              | 1/fs |

|                | 0.1667 ≤ FSO/FSI < 0.226       | GD     | -                    | 32       | -              | 1/fs |

|                | と出力の位相ずれがない時の「                 |        | <i>5</i> 4 3 4 4 4 5 |          | \\ \D_+ \   \L |      |

Note 12. 入力と出力の位相ずれがない時の、L, R のデータが入力された後の ILRCK の立ち上がりから、L, R データを出力する前の OLRCK の立ち上がりまでの期間です。

# ■ ショートディレイ・スローロールオフ・フィルタ特性

| Parameter            |                         | Symbol | Min.      | Тур. | Max.      | Unit |

|----------------------|-------------------------|--------|-----------|------|-----------|------|

| Digital Filter       |                         |        |           |      |           |      |

| Passband –0.01dB     | 0.1667≤FSO/FSI < 24.000 | PB     | 0         | -    | 0.0417FSI | kHz  |

| Stopband             | 0.1667≤FSO/FSI < 24.000 | SB     | 0.4167FSI | -    |           | kHz  |

| Passband Ripple      |                         | PR     | -         | -    | ±0.01     | dB   |

| Stopband Attenuation | SA                      | -      | 108.1     | -    | dB        |      |

| Group Delay (Note    | 12)                     | GD     | -         | 21   | -         | 1/fs |

Note 12. 入力と出力の位相ずれがない時の、L, R のデータが入力された後の ILRCK の立ち上がりから、L, R データを出力する前の OLRCK の立ち上がりまでの期間です。

#### 11. DSD モード特性

#### ■ シャープロールオフ・フィルタ特性

(Ta=-40~ +105°C; DVDD=3.0~3.6V or DVDD=DV18=1.7V~1.9V; DVSS=0V, ILRCK=48kHz)

| Parameter            |            |      |           | Symbol | Min. | Тур. | Max. | Unit |

|----------------------|------------|------|-----------|--------|------|------|------|------|

| Digital Filter       | •          |      |           |        |      |      |      |      |

| Passband             | PCMFSO bit | "00" | -0.24dB   | PB     | 0    | -    | 20   | kHz  |

|                      | PCMFSO bit | "01" | -1.04dB   | PB     | 0    | -    | 40   | kHz  |

|                      | PCMFSO bit | "10" | -3.86dB   | PB     | 0    | -    | 80   | kHz  |

|                      | PCMFSO bit | "11" | -5.90dB   | PB     | 0    | -    | 100  | kHz  |

| Stopband             | PCMFSO bit | "00" | -         | SB     | 46   | -    | -    | kHz  |

|                      | PCMFSO bit | "01" | -         | SB     | 66   | -    | -    | kHz  |

|                      | PCMFSO bit | "10" | -         | SB     | 86   | -    | -    | kHz  |

|                      | PCMFSO bit | "11" | -         | SB     | 126  | -    | -    | kHz  |

|                      | PCMFSO bit | "00" | -         | PR     | -    | -    | ±0.2 | dB   |

| Passband             | PCMFSO bit | "01" | -         | PR     | -    | -    | ±0.5 | dB   |

| Ripple               | PCMFSO bit | "10" | -         | PR     | -    | -    | ±2.0 | dB   |

|                      | PCMFSO bit | "11" | -         | PR     | -    | -    | ±3.0 | dB   |

| Stopband Attenuation |            |      | SA        | -      | 112  | -    | dB   |      |

| Group Delay          |            | (    | (Note 15) | GD     | -    | 15   | -    | 1/fs |

Note 13. SACD フォーマットブック(Scarlet Book)では、DSD 信号のピークレベルがデューティレンジ 25%~75%を越えることは推奨されていません。

Note 14. 入力に 1kHz、デューティレンジ 25%~75%の sine 波を与えたときの出力レベルを 0dB とします。 Note 15. Group Delay は PCM 出力(44.1kHz or 48kHz)のとき

#### ■ スローロールオフ・フィルタ特性

(Ta=-40~ +105°C; DVDD=3.0~3.6V or DVDD=DV18=1.7V~1.9V; DVSS=0V, ILRCK=48kHz)

| Parameter             | Symbol | Min. | Тур. | Max.  | Unit |

|-----------------------|--------|------|------|-------|------|

| Digital Filter        |        |      |      |       |      |

| Passband -0.28dB      | PB     | 0    | -    | 10    | kHz  |

| Stopband              | SB     | 156  | -    | -     | kHz  |

| Passband Ripple       | PR     | -    | -    | ±0.15 | dB   |

| Stopband Attenuation  | SA     | •    | 112  | -     | dB   |

| Group Delay (Note 15) | GD     | -    | 15   | -     | 1/fs |

Note 13. SACDフォーマットブック(Scarlet Book)では、DSD信号のピークレベルがデューティレンジ 25%~75%を越えることは推奨されていません。

Note 14. 入力に1kHz、デューティレンジ25%~75%のsine波を与えたときの出力レベルを0dBとします。

Note 15. Group DelayはPCM出力(44.1kHz or 48kHz)のとき

# ■ ショートディレイ・シャープロールオフ・フィルタ特性

(Ta=-40~ +105°C; DVDD=3.0~3.6V or DVDD=DV18=1.7V~1.9V; DVSS=0V, ILRCK=48kHz)

| Parameter            |            |      |         | Symbol | Min. | Тур. | Max. | Unit |

|----------------------|------------|------|---------|--------|------|------|------|------|

| Digital Filter       | •          |      |         |        |      |      |      |      |

| Passband             | PCMFSO bit | "00" | -0.24dB | PB     | 0    | -    | 20   | kHz  |

|                      | PCMFSO bit | "01" | -1.04dB | PB     | 0    | -    | 40   | kHz  |

|                      | PCMFSO bit | "10" | -3.86dB | PB     | 0    | -    | 80   | kHz  |

|                      | PCMFSO bit | "11" | -5.90dB | PB     | 0    | -    | 100  | kHz  |

| Stopband             | PCMFSO bit | "00" | -       | SB     | 46   | -    | -    | kHz  |

|                      | PCMFSO bit | "01" | -       | SB     | 66   | -    | -    | kHz  |

|                      | PCMFSO bit | "10" | -       | SB     | 86   | -    | -    | kHz  |

|                      | PCMFSO bit | "11" | -       | SB     | 126  | -    | -    | kHz  |

|                      | PCMFSO bit | "00" | -       | PR     | -    | -    | ±0.2 | dB   |

| Passband             | PCMFSO bit | "01" | -       | PR     | -    | -    | ±0.5 | dB   |

| Ripple               | PCMFSO bit | "10" | -       | PR     | -    | -    | ±2.0 | dB   |

|                      | PCMFSO bit | "11" | -       | PR     | -    | -    | ±3.0 | dB   |

| Stopband Attenuation |            | SA   | •       | 112    | -    | dB   |      |      |

| Group Delay          |            | (No  | ote 15) | GD     | -    | 13   | -    | 1/fs |

Note 13. SACDフォーマットブック(Scarlet Book)では、DSD信号のピークレベルがデューティレンジ 25%~75%を越えることは推奨されていません。

Note 14. 入力に1kHz、デューティレンジ25%~75%のsine波を与えたときの出力レベルを0dBとします。

Note 15. Group Delay は PCM 出力(44.1kHz or 48kHz)のとき

### ■ ショートディレイ・スローロールオフ・フィルタ特性

(Ta=-40~ +105°C; DVDD=3.0~3.6V or DVDD=DV18=1.7V~1.9V; DVSS=0V, ILRCK=48kHz)

| Parameter            |           | Symbol | Min. | Тур. | Max.  | Unit |

|----------------------|-----------|--------|------|------|-------|------|

| Digital Filter       |           |        |      |      |       |      |

| Passband -0.28dB     |           | PB     | 0    | -    | 10    | kHz  |

| Stopband             |           | SB     | 156  | -    | -     | kHz  |

| Passband Ripple      |           | PR     | -    | -    | ±0.15 | dB   |

| Stopband Attenuation |           | SA     | -    | 112  | -     | dB   |

| Group Delay          | (Note 15) | GD     |      | 13   | -     | 1/fs |

Note 13. SACDフォーマットブック(Scarlet Book)では、DSD信号のピークレベルがデューティレンジ 25%~75%を越えることは推奨されていません。

Note 14. 入力に1kHz、デューティレンジ25%~75%のsine波を与えたときの出力レベルを0dBとします。

Note 15. Group DelayはPCM出力(44.1kHz or 48kHz)のとき

# 12. 入出力組み合わせ例

入力データと出力データの可能な、組み合わせを示します。 Fsi は入力データのサンプルレート、Fso は出力データのサンプルレートです。

| Fsi[KHz] | Fso[ | KHz]  | Fso[MHz] |        |         |  |

|----------|------|-------|----------|--------|---------|--|

| PCM      | PC   | PCM   |          | DCD    |         |  |

| PCIVI    | min  | max   | DSD      |        |         |  |

| 8        | 8    | 192   | -        | -      | -       |  |

| 11.025   | 8    | 264.6 | -        | -      | -       |  |

| 16       | 8    | 384   | -        | -      | -       |  |

| 32       | 8    | 768   | -        | -      | -       |  |

| 44.1     | 8    | 768   | 2.8224   | 5.6448 | ı       |  |

| 48       | 8    | 768   | 2.8224   | 5.6448 | -       |  |

| 88.2     | 14.7 | 768   | 2.8224   | 5.6448 | -       |  |

| 96       | 16   | 768   | 2.8224   | 5.6448 | -       |  |

| 176.4    | 29.6 | 768   | 2.8224   | 5.6448 | 11.2896 |  |

| 192      | 32   | 768   | 2.8224   | 5.6448 | 11.2896 |  |

| Fsi[MHz] | Fso[ | KHz] |        | Fso[MHz] |         |

|----------|------|------|--------|----------|---------|

| DeD      | PC   | CM   | DeD    |          |         |

| DSD      | min  | max  | DSD    |          |         |

| 2.8224   | 44.1 | 768  | 2.8224 | 5.6448   | 11.2896 |

| 5.6448   | 44.1 | 768  | 2.8224 | 5.6448   | 11.2896 |

| 11.2896  | 44.1 | 768  | 2.8224 | 5.6448   | 11.2896 |

| Fsi[KHz] | Fso[ | KHz] |       | Fso[MHz] |        |  |

|----------|------|------|-------|----------|--------|--|

| PCM      | PC   | PCM  |       | D0D      |        |  |

| PCIVI    | min  | max  |       | DSD      |        |  |

| 8        | 8    | 192  | -     | -        | -      |  |

| 12       | 8    | 288  | -     | •        | -      |  |

| 16       | 8    | 384  | -     | •        | -      |  |

| 32       | 8    | 768  | -     | ı        | ı      |  |

| 44.1     | 8    | 768  | 3.072 | 6.144    | -      |  |

| 48       | 8    | 768  | 3.072 | 6.144    | -      |  |

| 88.2     | 14.7 | 768  | 3.072 | 6.144    | -      |  |

| 96       | 16   | 768  | 3.072 | 6.144    | -      |  |

| 176.4    | 29.6 | 768  | 3.072 | 6.144    | -      |  |

| 192      | 32   | 768  | 3.072 | 6.144    | 12.288 |  |

| Fsi[MHz] | Fso[ | KHz] |       | Fso[MHz] |        |

|----------|------|------|-------|----------|--------|

| DCD      | PC   | CM   | DSD   |          |        |

| DSD      | min  | max  |       |          |        |

| 3.072    | 48   | 768  | 3.072 | 6.144    | 12.288 |

| 6.144    | 48   | 768  | 3.072 | 6.144    | 12.288 |

| 12.288   | 48   | 768  | 3.072 | 6.144    | 12.288 |

下記組み合わせはダウンコンバートした場合、歪特性が 80dB 程度になる場合があります。

| Fsi[KHz] | Fso[    | KHz] | Fso[MHz] |        |         |  |

|----------|---------|------|----------|--------|---------|--|

| DCM      | PC      | CM   | DCD      |        |         |  |

| PCM      | min     | max  | DSD      |        |         |  |

| 384      | 64~384  | 768  | 2.8224   | 5.6448 | 11.2896 |  |

| 768      | 128~768 | 768  | 2.8224   | 5.6448 | 11.2896 |  |

| Fsi[KHz] | Fso[    | KHz] | Fso[MHz] |       |        |  |

|----------|---------|------|----------|-------|--------|--|

| DCM      | PC      | CM   | Den      |       |        |  |

| PCM      | min     | max  | DSD      |       |        |  |

| 384      | 64~384  | 768  | 3.072    | 6.144 | 12.288 |  |

| 768      | 128~768 | 768  | 3.072    | 6.144 | 12.288 |  |

### 13. DC 特性

(Ta=-40~ +105°C; DVDD=3.0~3.6V VSEL = "L" or DVDD=DV18=1.7V~1.9V: VSEL = "H")

| Parameter                    | Symbol | Min.     | Тур. | Max.    | Unit |

|------------------------------|--------|----------|------|---------|------|

| High-Level Input Voltage     | VIH    | 70%DVDD  | -    | -       | V    |

| Low-Level Input Voltage      | VIL    | -        | -    | 30%DVDD | V    |

| High-Level Output Voltage    |        |          |      |         |      |

| Except SDA pin (lout=-400μA) | VOH    | DVDD-0.4 | -    | -       | V    |

| Low-Level Output Voltage     |        |          |      |         |      |

| Except SDA pin (lout=400μA)  | VOL    | -        | -    | 0.4     | V    |

| SDA pin (lout=3mA)           | VOL    |          |      | 0.4     | V    |

| Input Leakage Current        | lin    | -        | -    | ±10     | μΑ   |

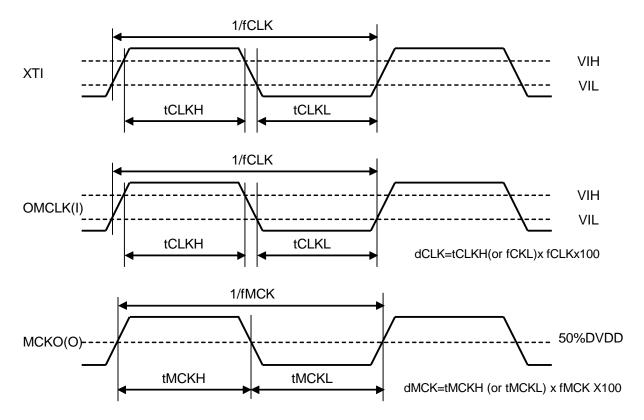

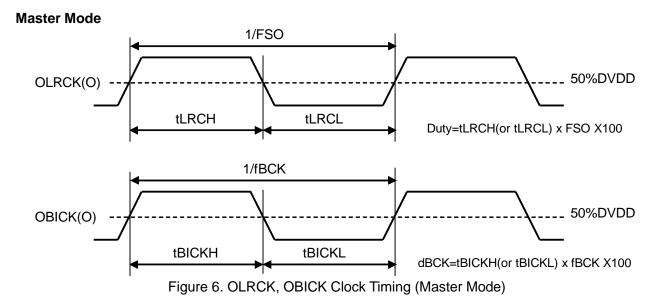

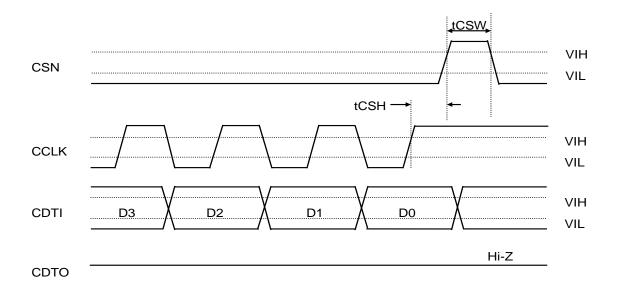

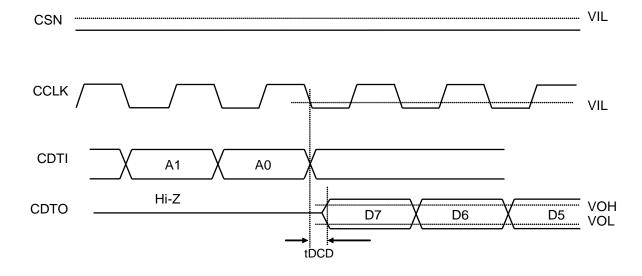

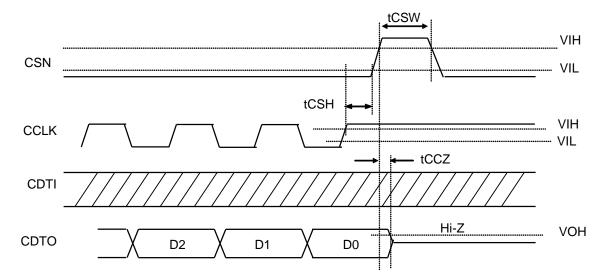

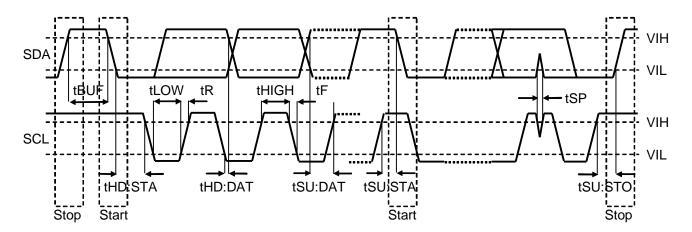

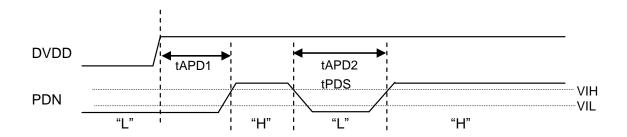

# 14. スイッチング特性

$(Ta=-40~+105^{\circ}C; DVDD=3.0~3.6V: VSEL = "L" or DVDD=DV18=1.7V~1.9V: VSEL = "H"; C_L=20pF)$

| Parameter                     | Symbol | Min.    | Тур. | Max.   | Unit |

|-------------------------------|--------|---------|------|--------|------|

| Master Clock Timing           |        |         |      |        |      |

| Crystal Oscillator Frequency  | fXTAL  | 11.2896 |      | 24.576 | MHz  |

| (44.1, 48, 88.2, 96KHz の256倍) |        |         |      |        |      |

| OMCLK Input                   |        |         |      |        |      |

| 64 FSO :                      | fCLK   | 0.512   |      | 49.152 | MHz  |

| Pulse Width Low               | tCLKL  | 7       |      |        | ns   |

| Pulse Width High              | tCLKH  | 7       |      |        | ns   |

| 128 FSO :                     | fCLK   | 1.024   |      | 49.152 | MHz  |

| Pulse Width Low               | tCLKL  | 7       |      |        | ns   |

| Pulse Width High              | tCLKH  | 7       |      |        | ns   |

| 256 FSO :                     | fCLK   | 2.048   |      | 49.152 | MHz  |

| Pulse Width Low               | tCLKL  | 7       |      |        | ns   |

| Pulse Width High              | tCLKH  | 7       |      |        | ns   |

| 384 FSO :                     | fCLK   | 3.072   |      | 36.864 | MHz  |

| Pulse Width Low               | tCLKL  | 10      |      |        | ns   |

| Pulse Width High              | tCLKH  | 10      |      |        | ns   |

| 512 FSO :                     | fCLK   | 4.096   |      | 49.152 | MHz  |

| Pulse Width Low               | tCLKL  | 7       |      |        | ns   |

| Pulse Width High              | tCLKH  | 7       |      |        | ns   |

| 768 FSO :                     | fCLK   | 6.144   |      | 36.864 | MHz  |

| Pulse Width Low               | tCLKL  | 10      |      |        | ns   |

| Pulse Width High              | tCLKH  | 10      |      |        | ns   |

| MCKO Output                   |        |         |      |        |      |

| Frequency                     | fMCK   | 0.512   |      | 49.152 | MHz  |

| Duty (Note 16)                | dMCLK  | 40      | 50   | 60     | %    |

Note 16. 出力ポートのマスタクロックを水晶振動子で供給する場合の MCKO 出力 Duty の仕様です。

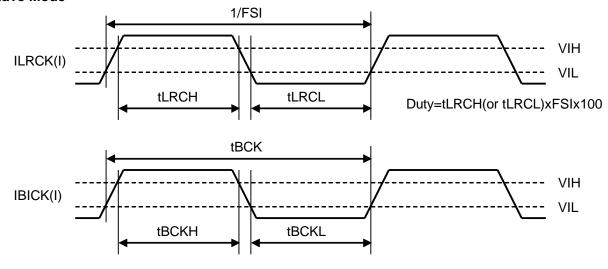

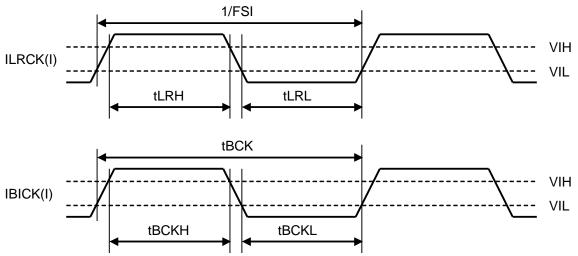

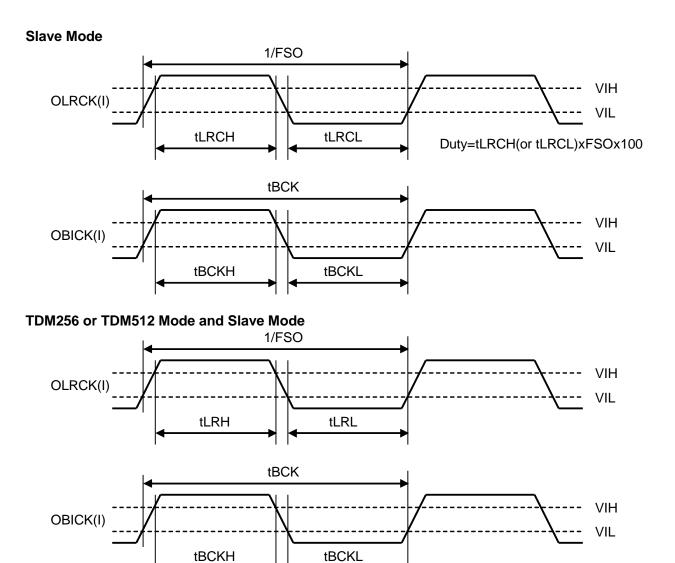

| Parameter                             | Symbol | Min.      | Тур. | Max. | Unit |

|---------------------------------------|--------|-----------|------|------|------|

| Input PORT ILRCK                      |        |           |      |      |      |

| Frequency                             |        |           |      |      | kHz  |

| Normal speed mode                     | FSIN   | 8         |      | 54   | kHz  |

| Double speed mode                     | FSID   | 54        |      | 108  | kHz  |

| Quad speed mode                       | FSIQ   | 108       |      | 216  | kHz  |

| Oct speed mode                        | FSIO   |           | 384  |      | kHz  |

| Hex speed mode                        | FSIH   |           | 768  |      | kHz  |

| Duty Cycle Slave Mode                 | Duty   | 48        | 50   | 52   | %    |

| Output PORT OLRCK                     |        |           |      |      |      |

| Frequency                             |        |           |      |      |      |

| Slave mode                            |        |           |      |      |      |

| Normal speed mode                     | FSON   | 8         |      | 54   | kHz  |

| Double speed mode                     | FSOD   | 54        |      | 108  | kHz  |

| Quad speed mode                       | FSOQ   | 108       |      | 216  | kHz  |

| Oct speed mode                        | FSOO   |           | 384  |      | kHz  |

| Hex speed mode                        | FSOH   |           | 768  |      | kHz  |

| Master mode, OMCLK Input, 64FSO mode  | FSO    | 8         |      | 768  | kHz  |

| Master mode, OMCLK Input, 128FSO mode | FSO    | 8         |      | 384  | kHz  |

| Master mode, OMCLK Input, 256FSO mode | FSO    | 8         |      | 192  | kHz  |

| Master mode, OMCLK Input, 384FSO mode | FSO    | 8         |      | 96   | kHz  |

| Master mode, OMCLK Input, 512FSO mode | FSO    | 8         |      | 96   | kHz  |

| Master mode, OMCLK Input, 768FSO mode | FSO    | 8         |      | 48   | Khz  |

| Duty Cycle                            |        |           |      |      |      |

| Slave Mode                            | Duty   | 48        | 50   | 52   | %    |

| Master Mode                           | Duty   |           | 50   |      | %    |

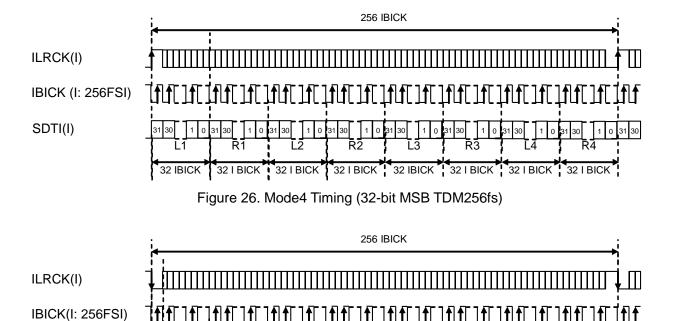

| Input PORT ILRCK for TDM256 Mode      |        |           |      |      |      |

| Frequency                             | FSI    | 8         |      | 96   | kHz  |

| "H" time (slave mode)                 | tLRH   | 1/256FSI  |      |      | ns   |

| "L" time (slave mode)                 | tLRL   | 1/256FSI  |      |      | ns   |

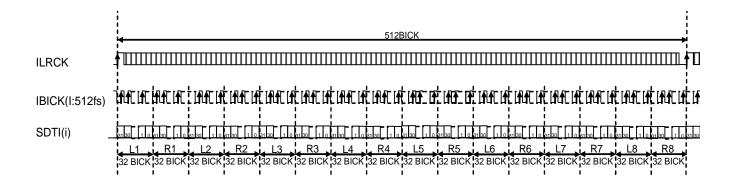

| Input PORT ILRCK for TDM512 Mode      |        |           |      |      |      |

| Frequency                             | FSI    | 8         |      | 48   | kHz  |

| "H" time (slave mode)                 | tLRH   | 1/512FSI  |      |      | ns   |

| "L" time (slave mode)                 | tLRL   | 1/512FSI  |      |      | ns   |

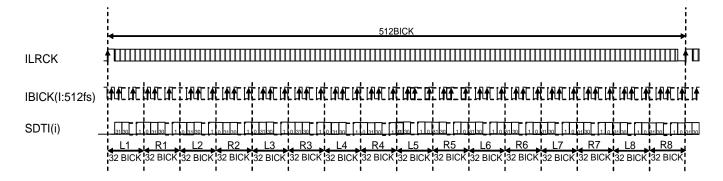

| Output PORT OLRCK for TDM256 Mode     |        |           |      |      |      |

| Frequency                             | FSO    | 8         |      | 96   | kHz  |

| "H" time (slave mode)                 | tLRH   | 1/256 FSO |      |      | ns   |

| "L" time (slave mode)                 | tLRL   | 1/256 FSO |      |      | ns   |

| Output PORT OLRCK for TDM512 Mode     |        |           |      |      |      |

| Frequency                             | FSO    | 8         |      | 48   | kHz  |

| "H" time (slave mode)                 | tLRH   | 1/512 FSO |      |      | ns   |

| "L" time (slave mode)                 | tLRL   | 1/512 FSO |      |      | ns   |

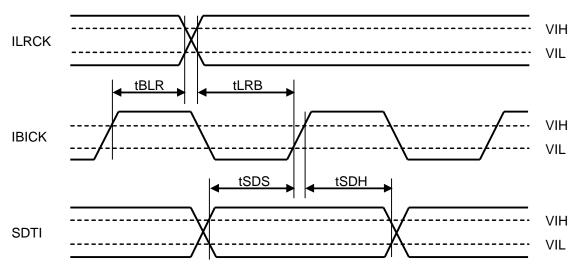

| Parameter                                                       | Symbol       | Min.       | Тур.       | Max. | Unit     |

|-----------------------------------------------------------------|--------------|------------|------------|------|----------|

| Audio Interface Timing                                          |              |            |            |      |          |

| Input PORT (Slave mode)                                         |              |            |            |      |          |

| IBICK Period Normal speed mode                                  | tBCK         | 1/256 FSIN |            |      | ns       |

| Double speed mode                                               | tBCK         | 1/128 FSID |            |      | ns       |

| Quad speed mode                                                 | tBCK         | 1/64 FSIQ  |            |      | ns       |

| Oct speed mode                                                  | tBCK         | 1/64 FSIO  |            |      | ns       |

| Hex speed mode                                                  | tBCK         | 1/64 FSIH  |            |      | ns       |

| IBICK Pulse Width Low                                           | tBCKL        | 7          |            |      | ns       |

| Pulse Width High                                                | tBCKH        | 7          |            |      | ns       |

| ILRCK Edge to IBICK "↑" (Note 17)                               | tLRB<br>tBLR | 5          |            |      | ns       |

| IBICK "↑" to ILRCK Edge (Note 17) SDTI Hold Time from IBICK "↑" | tSDH         | 5<br>5     |            |      | ns       |

| SDTI Hold Time from IBICK   SDTI Setup Time to IBICK "↑"        | tSDS         | 5          |            |      | ns<br>ns |

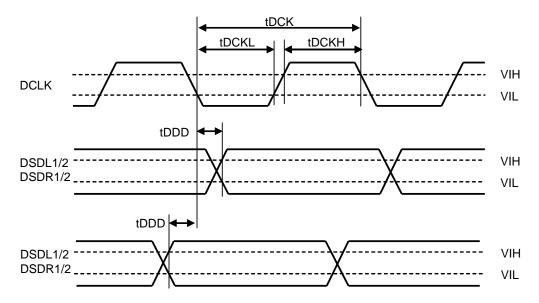

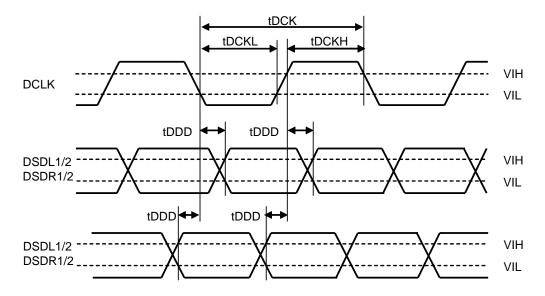

| DSD Audio Interface Timing (64 mode)                            | 1000         | <u> </u>   |            |      | 113      |

| IDCLK Period                                                    | tDCK         |            | 1/64FSIN   |      | ns       |

| IDCLK Pellod IDCLK Pulse Width Low                              | tDCKL        | 160        | 1/041 3111 | -    |          |

|                                                                 |              |            |            |      | ns       |

| IDCLK Pulse Width High                                          | tDCKH        | 160        |            | 00   | ns       |

| IDCLK Edge to DSDL/R                                            | tDDD         | -20        |            | 20   | ns       |

| DSD Audio Interface Timing (128 mode)                           | 10014        |            | 4/4005011  |      |          |

| IDCLK Period                                                    | tDCK         | -          | 1/128FSIN  | -    | ns       |

| IDCLK Pulse Width Low                                           | tDCKL        | 80         |            |      | ns       |

| IDCLK Pulse Width High                                          | tDCKH        | 80         |            |      | ns       |

| IDCLK Edge to DSDL/R                                            | tDDD         | -10        |            | 10   | ns       |

| DSD Audio Interface Timing (256 mode)                           |              |            |            |      |          |

| IDCLK Period                                                    | tDCK         | -          | 1/256FSIN  | -    | ns       |

| IDCLK Pulse Width Low                                           | tDCKL        | 40         |            |      | ns       |

| IDCLK Pulse Width High                                          | tDCKH        | 40         |            |      | ns       |

| IDCLK Edge to DSDL/R                                            | tDDD         | <b>-</b> 5 |            | 5    | ns       |

| Input PORT (TDM256 slave mode)                                  |              |            |            |      |          |

| IBICK Period                                                    | tBCK         | 40         |            |      | ns       |

| IBICK Pulse Width Low                                           | tBCKL        | 16         |            |      | ns       |

| Pulse Width High                                                | tBCKH        | 16         |            |      | ns       |

| ILRCK Edge to IBICK "↑" (Note 17)                               | tLRB         | 10         |            |      | ns       |

| IBICK "↑" to ILRCK Edge (Note 17)                               | tBLR         | 10         |            |      | ns       |

| SDTI Hold Time from IBICK "↑" SDTI Setup Time to IBICK "↑"      | tSDH<br>tSDS | 10<br>6    |            |      | ns<br>ns |

| Input PORT (TDM512 slave mode)                                  | เอยอ         | 0          |            |      | 115      |

| IBICK Period                                                    | tBCK         | 40         |            |      | ns       |

| IBICK Pulse Width Low                                           | tBCKL        | 16         |            |      | ns       |

| Pulse Width High                                                | tBCKH        | 16         |            |      | ns       |

| ILRCK Edge to IBICK "↑" (Note 17)                               | tLRB         | 10         |            |      | ns       |

| IBICK "↑" to ILRCK Edge (Note 17)                               | tBLR         | 10         |            |      | ns       |

| SDTI Hold Time from IBICK "↑"                                   | tSDH         | 10         |            |      | ns       |

| SDTI Setup Time to IBICK "↑"                                    | tSDS         | 6          |            |      | ns       |

Note 17. この規格値は ILRCK のエッジと IBICK の"↑"が重ならないように規定しています。 Note 18. IBICK, OBICK の Max 周波数:49.152MHz

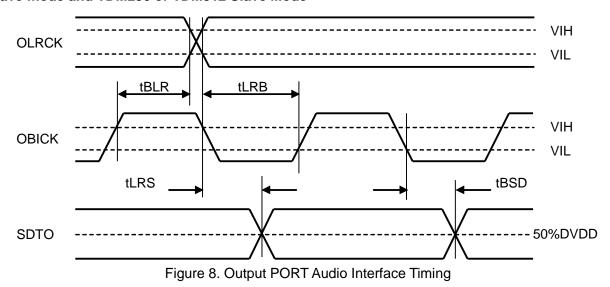

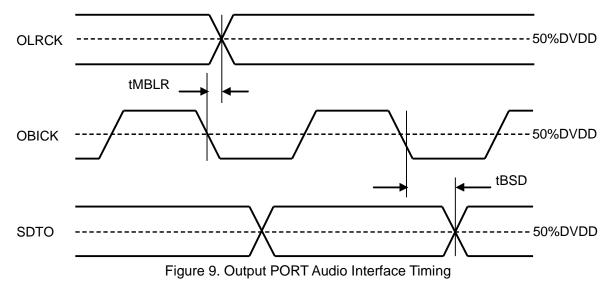

| Parameter                                                                                                                        | Symbol                               | Min.                                                            | Тур.       | Max.     | Unit                 |

|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------|------------|----------|----------------------|

| Audio Interface Timing                                                                                                           |                                      |                                                                 |            |          |                      |

| Output PORT (Slave mode)                                                                                                         |                                      |                                                                 |            |          |                      |

| OBICK Period Normal speed mode Double speed mode Quad speed mode Oct speed mode Hex speed mode                                   | tBCK<br>tBCK<br>tBCK<br>tBCK<br>tBCK | 1/256 FSON<br>1/128 FSOD<br>1/64 FSOQ<br>1/64 FSOO<br>1/64 FSOH |            |          |                      |

| OBICK Pulse Width Low Pulse Width High OLRCK Edge to OBICK "↑" (Note 17) OBICK "↑" to OLRCK Edge (Note 17)                       | tBCKL<br>tBCKH<br>tLRB<br>tBLR       | 7<br>7<br>10<br>7                                               |            |          | ns<br>ns<br>ns<br>ns |

| DVDD=3.0V~3.6V(VSEL pin= "L") (fso=768KHz) OBICK "↓" to SDTO (HEXAE bit= "1")                                                    | tBSD                                 |                                                                 |            | 5        | ns                   |

| DVDD=3.0V~3.6V(VSEL pin= "L") (Except fso=768KHz) OLRCK to SDTO(MSB) (Except I <sup>2</sup> S mode) OBICK "↓" to SDTO            | tLRS<br>tBSD                         |                                                                 |            | 10<br>10 | ns<br>ns             |

| DVDD=1.7V~1.9V(VSEL pin= "H")  (Except fso=384KHz,768KHz)  OLRCK to SDTO(MSB) (Except I <sup>2</sup> S mode)  OBICK "\_" to SDTO | tLRS<br>tBSD                         |                                                                 |            | 20<br>20 | ns<br>ns             |

| DSD Audio Interface Timing (64 mode slave)                                                                                       |                                      |                                                                 |            |          |                      |